xilinx ug583

Xilinx ultrascale plus product table

Mar 16, · UltraScale+ FPGA Product Tables and Product Selection Guide(XMP103) ultrascale-plus-fpga-product-selection-guide.pdf Document_ID XMP103 Release_Date 2021-03-16 Revision. "/>

Learn MoreUG583 DDR impedance - Xilinx

Hello @arpi_10das9 ,I’m not fully understand your questions, but we recommend that please follow the Table 2-11 as much as possible. Xilinx evaluates the PCB based on the UG583.

Learn MorePS_INIT_B, PS_PROG_B, and PS_DONE - docs.xilinx.com

UG583 Release Date 2022-07-27 Revision 1.24 English UltraScale Architecture PCB Design User Guide Power Distribution System in UltraScale Devices Introduction to UltraScale Architecture Introduction PCB Decoupling Capacitors Recommended PCB Capacitors per Device Step Load Assumptions

Learn MoreUG583 UltraScale PCB Design

UltraScale Architecture PCB Design www.xilinx.com 2 UG583 (v1.1) August 28, Revision History The following table shows the revision history for this document. Date Version Revision

Learn MoreUSB Debug Guide for Zynq UltraScale+ and Versal Devices

Review PCB layout - Refer to Xilinx pcb guidelines recommendations. ZynqMP - https://www.xilinx.com/support/documentation/user_guides/ug583-

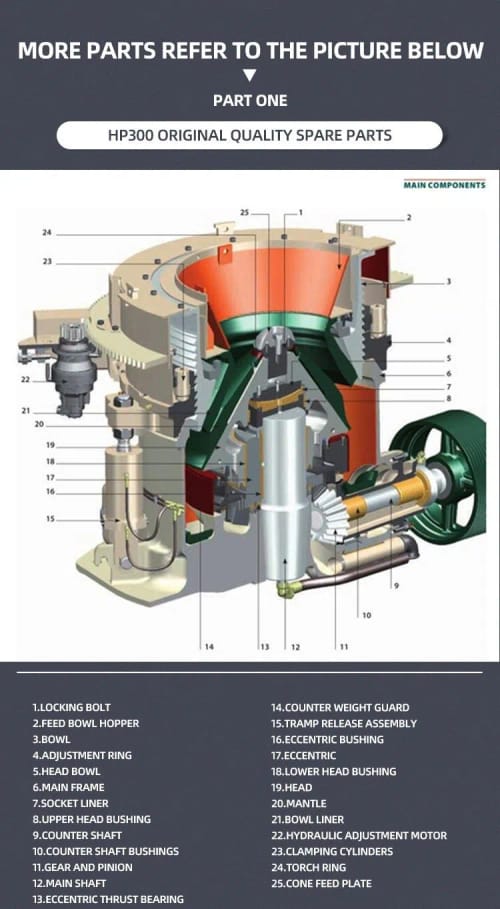

Learn MoreHP300 MAIN FRAME ASSY STD parts catalogue xilinx ug583

Volkswagen Golf Mk7 The ride height is 20 mm lower than the standard Golf. Golf R models equipped with the optional 'DCC' (Dynamic Chassis Control), offer three suspension Main Frame Price, Main Frame Price Manufacturers Main Frame Price - Select

Learn MoreXilinx pg203. MA102 Replaced CD with CK in Figure 2-7

体系」とは何赛灵思Xilinx PG203 - UltraScale+ Integrated 100G Ethernet Thurgood Marshall 2 UG583 (v1 248 10) January 30, www com:Xilinx 提供广泛

Learn Moreメモリ インターフェイス - UltraScale DDR4/DDR3

メモリ インターフェイス デザイン ハブ - UltraScale DDR3/DDR4 メモリ. 日本語版の列に示されている資料によっては、英語版の更新に対応していないものがあります。. 日本語版は参考用としてご使用の上、最新の情報につきましては、必ず最新英語版をご参照

Learn MoreXilinx zynq ultrascale - etsjy.teenice.shop

November 8, at 9:40 AM. ZYNQ Ultrascale+ Howto reset the PL. Hi, Through 1055 pages of UG1085, I do not find one location which clearly describes how I can do a very simple task of enabling the PLRESET0 signal going from APU to the PL. Basically I find related descriptions in two locations in the document, none of them give you any clue on.

Learn More쉽게 배우는 DDR4(DIMM) PCB 설계(3

Easy DDR4(DIMM) PCB Design(3) - Signals. DDR4의 신호선을 더 알아보자. 참고할 데이타시트는 칩 제조회사인 자일링스(Xilinx)의 UG583 문서다.

Learn More8 Synopsys Xilinx jobs in Hillsboro, Oregon, United States (1 new

Today's top 8 Synopsys Xilinx jobs in Hillsboro, Oregon, United States. Leverage your professional network, and get hired. New Synopsys Xilinx jobs added daily.

Learn Morerhino convert mesh to surface - rbazda.3waystoearnincomeathome.info

PCB Guidelines for the PS Interface in the Zynq UltraScale+ MPSoC UltraScale Architecture PCB Design User Guide (UG583) Document ID UG583 Release Date 2022-04-14 Revision 1.23 English. UltraScale Architecture PCB Design User Guide. dayz steam charts. Press enter

Learn MoreIntegrated Power Supply Reference Design for Xilinx® Zynq

using the Xilinx Zynq Ultrascale+ (ZU+) MPSoC devices. The 10 ZU+ products that can Power Devices in Xilinx document UG583. • Similarly to Variant 002,

Learn MoreUltrascale ethernet - srtm.maverickinter.shop

The act of processing the communication protocol stack at 10 Gigabit Ethernet, taxes modern FPGAs to cater high-speed network applications. Engineers who're designing the solutions around 10GbE got a helping hand from the introduction of Xilinx Zynq UltraScale+ MPSoC.

Learn MoreLead FPGA Design Engineer -C/C++, Xilinx - FPGA, Hardware, VHDL

Xilinx VHDL/Verilog development So, if you are a Senior or Lead FPGA Design Engineer -C/C++, Xilinx with experience, please apply today! Email Your Resume In Word To Looking forward to receiving your resume through our website and going over the position with you. Clicking apply is the best way to apply, but you may also: Maria.Reyes@

Learn MorePDF UltraScale Architecture Configurable Logic Block User Guide ... - XilinxPDF

The UltraScale architecture CLBs provide advanced, high-performance, low-power programmable logic with: • Real 6-input look-up table (LUT) capability. • Dual LUT5 (5-input LUT) option. • Distributed memory and shift register logic (SRL) ability. • Dedicated high-speed carry logic for arithmetic functions.

Learn MoreRecommended Decoupling Capacitor Quantities for Artix

2022/7/27 · Recommended Decoupling Capacitor Quantities for Artix UltraScale+ , Kintex UltraScale+ , and Virtex UltraScale+ Devices UltraScale Architecture PCB Design User Guide

Learn MoreZynqUSplus Power Cookbook 2pager

Xilinx may update UG583 where the VCCINT_VCU rail will be separated from the VCCBRAM rail to 0.9V; in this case Configurations 7 and 8, the ch C can be.

Learn MoreXilinx sgmii - afgppu.atbeauty.info

Free. Windows. ••• This program is designed to write a raw disk image to a removable device or backup a removable device to a raw image file. The Xilinx Ethernet Quad Serial Gigabit Media Independent Interface PCS/PMA or QSGMII IP LogiCORE™ IP provides an Ethernet Physical Coding Sublayer (PCS) with an aggregation of four 10/100/1000M ports to one five gigabit.

Learn MorePCN-20200511 - Confluence Mobile - Trenz Electronic Wiki

Reason: Xilinx recommondation UG583. Impact: DDR4-Alert signal pulled up to VCCO_PSDDR. #4 Added testpoints. Type: PCB. Reason: Improve for

Learn MoreXilinx ultrascale plus product table - undy.rajasan.de

aka boule 2024 location. Add entry to ARP table · Issue #56 · Xilinx/xup_vitis_network_example · GitHub. on Apr 22.FIR Compiler v7.2 www.xilinx.com 2 PG149 January 21, Table of Contents IP Facts Versal™ ACAP, UltraScale+™, UltraScale™, Zynq-7000 SoC 7 Series Supported User Interfaces AXI4-Stream Resources www.xilinx.com Chapter 2 Product Specification Performance

Learn MoreXilinx - Adaptable. Intelligent | together we advance_

Xilinx (now a part of AMD) is the inventor of the FPGA, programmable SoCs, and now, the ACAP & delivers the most dynamic processing technology in the industry.

Learn MoreXilinx rfsoc product table - argoj.pick-point.shop

The RF DC Evaluation Tool can be used to compare different scenario and settings of the Zynq® UltraScale+™ RFSoC ADCs and DACs. In these two examples, we compare a

Learn MoreXilinx sdr - gdv.madebyulla.de

Memory Interface is a free software tool used to generate memory controllers and interfaces for Xilinx ® FPGAs. Memory Interface generates unencrypted Verilog or VHDL design files, UCF constraints, 7 Digital Rotation Digital Rotation (DR) signals a revolution in image rotation and de-rotation.

Learn MoreUltraScale Architecture PCB Design User Guide (UG583) - Xilinx

2022/7/27 · Document ID. UG583. Release Date. 2022-07-27. Revision. 1.24 English. UltraScale Architecture PCB Design User Guide. Power Distribution System in UltraScale Devices.

Learn MoreUltraScale+ FPGA Product Tables and Product Selection Guide

Consult UG583, UltraScale Architecture PCB Design User Guide for specific all data in this document with the device data sheets found at www.xilinx.com.

Learn More

Leave a comment