stratix 10 emif user guide

EMIF on Stratix 10 Dev Kit miss board file - Intel Community

2018. 6. 22. · Hi all i'm working on EMIF for stratix 10 Dev KIT while generating the IP i can't find my board listed in the presets how can i add it

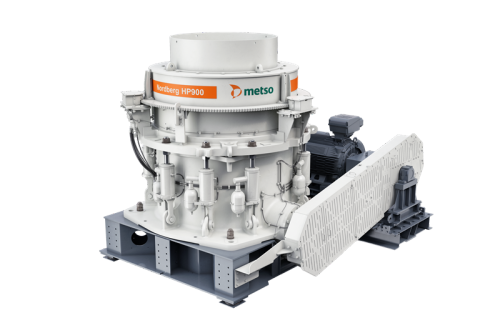

Learn MoreHP500 CNTRWGHT ASSY | stratix 10 emif user guide

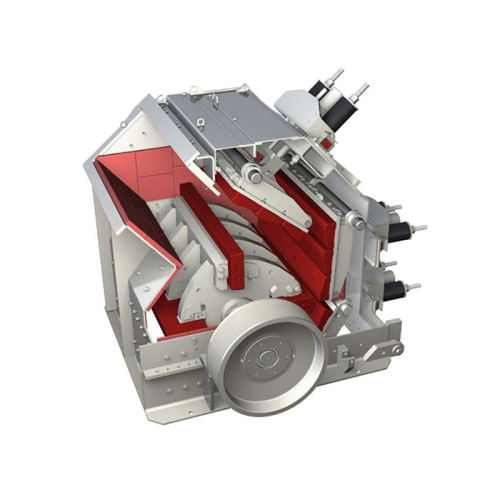

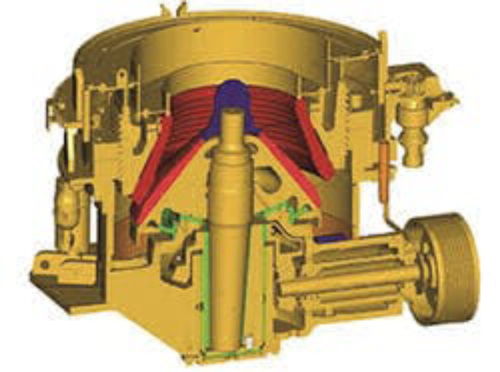

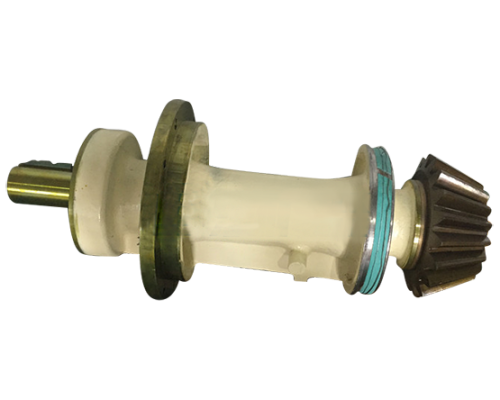

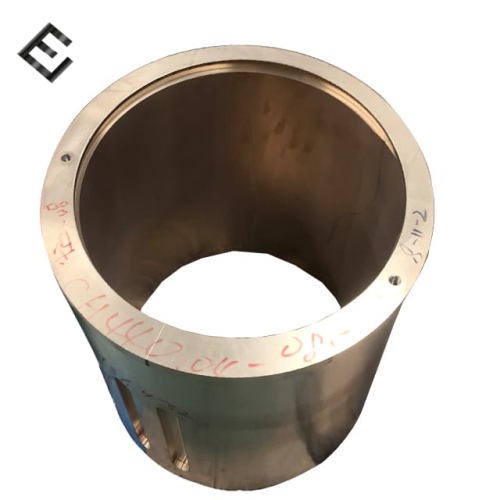

Cone crusher main shaft Jaw crusher main shaft. Part of the rotary movement in the machine is mounted on the shaft. Usually the cone crusher or jaw crusher have a main shaft and a pinion shaft.

Learn MoreExternal Memory Interfaces Intel® Cyclone® 10 GX FPGA IP

Design Example Quick Start Guide for External Memory Interfaces Intel Cyclone 10 GX FPGA IP .. Creating an EMIF Generating and Configuring the EMIF Intel

Learn More1.9. Debugging the Intel® Stratix® 10 EMIF Design Example

2022. 8. 24. · External Memory Interfaces Intel® Stratix® 10 FPGA IP Design Example User Guide. Download Bookmark. ID 683408. Date 3/29/2021. Version. Public. See Less. Visible

Learn MoreExternal Memory Interfaces Intel Stratix 10 FPGA IP Design Example User Guide

The Intel ® Stratix® 10 EMIF IP provides external memory interface support for DDR3, DDR4, QDR II/II+/Xtreme, QDR-IV, and RLDRAM 3 memory protocols. Search Intel® FPGAs and Programmable Devices / Documentation / External Memory Interfaces Intel Stratix 10

Learn MoreSY7SH O-RING stratix 10 emif user guide

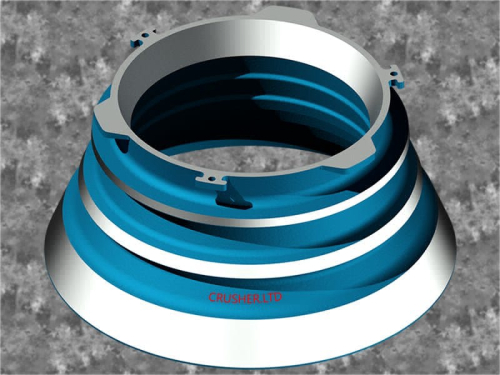

crusher liner user in australia stratix 10 emif user guide z036 hose los5-1aa25x2100 cone crusher internal eccentric bushing images metso. O-ring. An O-ring, also known as a packing or a toric joint, is a mechanical gasket in the shape of a torus; it is a loop of elastomer with a round cross-section, designed to be seated in a groove and

Learn MoreGP500S PIPE 42X3 K=175 stratix 10 emif user guide

Revestimientos de Seire GP Trituradora. pipe: 42x3 k=175: 0.41: mm0211573: sub-frame assembly / 0: mm0239996: eccentric shaft / 402: mm0252493: blower: hp

Learn MoreIntel Stratix 10 SoC FPGA Boot User Guide

2021. 11. 10. · Updated for Intel® Quartus® Prime Design Suite: 21.4. This user guide describes the Intel® Stratix® 10 SoC FPGA boot flow, boot sources, and configuration bitstream generation.

Learn MoreCentro de soporte de IP de interfaces de memoria externa - Intel

Video tutorial de estimación de especificaciones de EMIF. Herramientas de EMIF Intel Stratix 10 device pin-out y emiF address/command pin-out

Learn MoreStratix 10 External Memory Interface Pin Guidelines Quartus

0 ir 3 Stratix 10 EMIF Pin Guidelines are preliminary and subject to change Stratix 10 Devices section in the Stratix 10 General Purpose I/O User Guide:

Learn MoreExternal Memory Interface Handbook Volume 3: Reference

External Memory Interface Handbook Volume 3: Reference Material 2.4.8 Stratix 10 EMIF Architecture: PLL Reference Clock Networks.

Learn MoreArria 10 External Memory Interface Design Guidelines - DtSheet

9 Select 'Arria 10 External Memory Interfaces v13.1' IP under are preliminary and subject to change Arria 10 EMIF Timing paths User Logic (Core) 37

Learn More7.5.3.9. Stratix 10 EMIF IP DDR4 Parameters: Example Designs

2022. 7. 25. · General Pin-Out Guidelines for Stratix® 10 EMIF IP 1.3.2. Resource Sharing Guidelines for Stratix® 10 EMIF IP. 1.4. Core Logic and User Interface Data Rate 12.2. Hard

Learn MoreStratix 10 SoC - Configuring FPGA from HPS Design Example

Quick start guide · Allow the U-boot to load Linux and login using 'root' · Modify the prebuild script to executable and use it to configure FPGA

Learn MoreStratix 10 SoC GSRD | Documentation

2022. 8. 19. · Hard Memory Controller (HMC) for HPS External Memory Interface (EMIF) FPGA Peripherals connected to Lightweight HPS-to-FPGA (LWH2F) AXI Bridge and JTAG to Avalon Master Bridge . Three user LED please refer to Intel Stratix 10 SoC Boot User Guide and Intel Stratix 10 Hard Processor System Technical Reference Manual

Learn MoreExternal Memory Interfaces Intel® Cyclone® 10 GX FPGA IP

Configure the EMIF IP and click Generate Example Design in the upper-right corner of the window. 1. Design Example Quick Start Guide for

Learn MoreStratix 10 External Memory Interface Simulation Guidelines Quartus

2022. 7. 31. · Generating the EMIF IP Double-clicking on Stratix 10 External Memory Interfaces opens the IP Parameter Editor 2. Provide a File Name for the EMIF IP 3. Click Create 6. Configuring the EMIF IP 4. Under Memory Protocol, select the appropriate Protocol from the drop-down list 5. Under the General tab, select the desired Speed Grade and Memory

Learn More256 10 FPGA IP User Guide - Altera · PDF fileExternal Memory

External Memory Interfaces Intel® Stratix® 10 FPGA IP User Guide Updated for Intel® Quartus® Intel Stratix 10 EMIF Architecture: Input DQS Clock Tree.

Learn MoreExternal Memory Interface Handbook Volume 2: Design

To enable the data pin inversion feature, click Configuration Register Settings > Option Control in the Arria 10 EMIF IP. QDR IV SRAM devices also have a

Learn MoreExternal Memory Interfaces IP Support Center

For step-by-step instructions on how to daisy-chain multiple memory interfaces for compatibility with the EMIF Debug Toolkit, refer to the following user guide: Debugging Multiple Memory Interfaces guide The Read/Write 2-D Eye Diagram feature available in the EMIF Debug Toolkit generates read-and-write eye diagrams for each data pin.

Learn MoreGetting Started with Targeting Intel Quartus Pro Based Devices

This example is a step-by-step guide that helps you use the HDL Coder™ Create reference design for Intel Arria 10 SoC which uses the Early I/O feature.

Learn MoreEMIF DDR4 STRATIX 10 ,QUARTUS PRIME PRO 20.1 - Intel

2022. 1. 6. · Hi, I have Generated example design for emif stratix 10 and simulation scripts too. While simulating in the modelsim ,every signal has default values only. even calib_success&fail both were low only! one more thing ,I have generated emif core. With Avalon bus signal I am trying to feed some data,in this case aslo calibration is not going high.

Learn MoreExternal Memory Interfaces Intel® Stratix® 10 FPGA IP User

The Intel Stratix 10 EMIF IP provides external memory interface support for DDR3, DDR4, Intel Stratix 10 General Purpose I/O User Guide.

Learn MoreExternal Memory Interfaces Intel® Stratix® 10 FPGA IP Design Example User Guide

2021. 10. 25. · 1. Design Example Quick Start Guide for External Memory Interfaces Intel ® Stratix ® 10 FPGA IP. A new interface and more automated design example flow is available for Intel ® Stratix ® 10 external memory interfaces. The Example Designs tab in the parameter editor allows you to specify the creation

Learn More

Leave a comment